# Molybdenum Disulfide Nanoflake–Zinc Oxide Nanowire Hybrid Photoinverter

Seyed Hossein Hosseini Shokouh,<sup>‡</sup> Atiye Pezeshki,<sup>‡</sup> Syed Raza Ali Raza, Kyunghee Choi, Sung-Wook Min, Pyo Jin Jeon, Hee Sung Lee, and Seongil Im\*

Institute of Physics and Applied Physics, Yonsei University, Seoul 120-749, Korea. <sup>‡</sup>S. H. Hosseini Shokouh and A. Pezeshki contributed equally to this work.

**ABSTRACT** We demonstrate a hybrid inverter-type nanodevice composed of a MoS<sub>2</sub> nanoflake field-effect transistor (FET) and ZnO nanowire Schottky diode on one substrate, aiming at a one-dimensional (1D)–two-dimensional (2D) hybrid integrated electronic circuit with multifunctional capacities of low power consumption, high gain, and photodetection. In the present work, we used a nanotransfer printing method using polydimethylsiloxane for the fabrication of patterned bottom-gate MoS<sub>2</sub> nanoflake FETs, so that they could be placed near the ZnO nanowire Schottky diodes that were initially fabricated. The ZnO nanowire Schottky diode and MoS<sub>2</sub> FET worked respectively as load and driver for a logic inverter, which exhibits a high voltage gain of  $\sim 50$  at a supply voltage of 5 V and also shows a low power consumption of less than 50 nW. Moreover, our inverter effectively operates as a photoinverter, detecting visible photons, since MoS<sub>2</sub> FETs appear very photosensitive, while the serially connected ZnO nanowire Schottky diode was blind to visible light. Our 1D–2D hybrid nanoinverter would be quite promising for both logic and photosensing applications due to its performance and simple device configuration as well.

**KEYWORDS:** MoS<sub>2</sub> nanoflake FET · ZnO nanowire · photoinverter · Schottky diode · power consumption · nanotransfer printing

Two-dimensional (2D) materials are extremely interesting as building blocks of next-generation nanoelectronic devices because of their promising properties. The most widely studied two-dimensional material to date is graphene due to its high carrier mobility ( $\mu$ ) over 100 000 cm<sup>2</sup>/V·s,<sup>1,2</sup> but it has considerable limitations in regard to real device applications. In untreated form, graphene has no band gap, resulting in small current on/off ratios in field-effect transistors; graphene could hardly be used for switching circuits.<sup>3,4</sup> As one alternative 2D material beyond graphene, the molybdenum disulfide (MoS<sub>2</sub>) chalcogenide nanoflake recently appeared, circumventing the drawbacks of graphene (although its practical mobility is limited to a few hundred cm<sup>2</sup>/V·s).<sup>5,6</sup> Bulk MoS<sub>2</sub> is known to have an indirect band gap of  $\sim 1.2$  eV, although the few-angstrom-thin single-layered MoS<sub>2</sub> has been reported to exhibit a direct band gap of 1.8 eV.<sup>6–11</sup> The MoS<sub>2</sub> nanoflake has thus been investigated for field-effect transistors (FETs), photodetectors, and even logic circuits for NAND, NOR, small signal amplifiers, and ring oscillators.<sup>6,9,12–17</sup> However, good practical circuits using more

than two MoS<sub>2</sub>-based FETs generally need electron beam (e-beam) lithography for fabrication, since the nanoflakes of 2D MoS<sub>2</sub> are not large enough to pattern by photolithography. Therefore, 2D MoS<sub>2</sub>-based circuits are not that easy to realize by conventional photolithography on one substrate. Hence, a more favorable and simple way to use a MoS<sub>2</sub>-based device may be necessary.

Here, we report a bottom-up fabrication approach that uses quite a conventional method, to integrate different nanoscale building blocks for practical device applications. A MoS<sub>2</sub> nanoflake FET and a ZnO nanowire Schottky diode were coupled in series on the same substrate, to form an electric and photoelectric hybrid inverter. In fact, similar types of devices were very recently reported for a complementary inverter and gate-tunable p–n diode adopting MoS<sub>2</sub> and carbon nanotubes (CNTs),<sup>18,19</sup> but the incorporation of a ZnO nanowire device to a MoS<sub>2</sub> FET has not been reported yet. Such hybrid nanodevices would be novel because of their multifunctionalities; the properties of MoS<sub>2</sub> nanoflakes are different from those of ZnO nanowires, but

\* Address correspondence to semicon@yonsei.ac.kr.

Received for review March 3, 2014 and accepted April 9, 2014.

Published online April 09, 2014

10.1021/nn501230v

© 2014 American Chemical Society

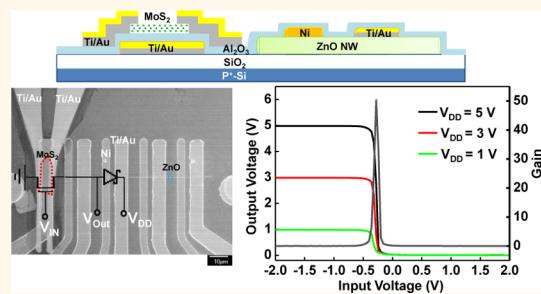

**Figure 1.** Schematics of the direct imprint (nanotransfer printing) process for the MoS<sub>2</sub> nanoflake FET–ZnO nanowire Schottky diode inverter: (a) MoS<sub>2</sub> exfoliation by PDMS, (b) selection of an optimally thin MoS<sub>2</sub> flake by utilizing a microscope, (c) nanotransfer printing of the chosen MoS<sub>2</sub> flake on the target site near the already fabricated ZnO nanowire diode, and (d) 3D view of the MoS<sub>2</sub> device placed near the ZnO nanowire Schottky diode; top contact Ti/Au forms the MoS<sub>2</sub> nanoflake FET, which will be connected to a Ni Schottky contact of the ZnO nanowire diode, so that finally an inverter forms on the same substrate.

both would be compensating each other. In the present study, we used such different but compensating properties to realize an electrical and photodetecting inverter. For a logic inverter, we used the MoS<sub>2</sub> FET for a high-speed switch, while the ZnO Schottky diode was used as a resistor for low power consumption or high voltage inverter gain. For a visible photodetecting inverter, a MoS<sub>2</sub> FET acts as a photosensitive switch due to the visible light-matching band gap of MoS<sub>2</sub>, while a ZnO nanowire Schottky diode acts as photo-blind resistor. For hybrid device processes, we developed a direct imprint (or nanotransfer printing) process and also utilized conventional photolithography, to place the MoS<sub>2</sub> flake near the ZnO nanowire as shown in Figure 1a–d. As a result, our inverter has been nicely fabricated as shown in Figure 2a–c, demonstrating a high voltage gain of ~50 and a low power consumption of 50 nW and also exhibiting good dynamic photoresponses in the visible range. More fabrication details involved with Figures 1 and 2 are found in the Methods section.

## RESULTS AND DISCUSSION

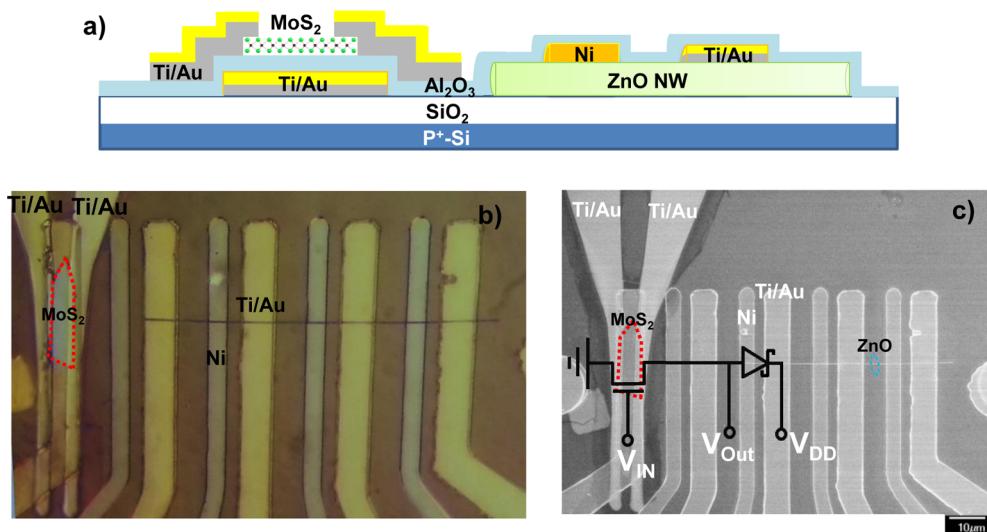

Figure 3a shows the linear and logarithmic scale current–voltage ( $I$ – $V$ ) characteristics of the ZnO nanowire Schottky diode, where 1  $\mu$ A is observed as on-current at 3 V forward bias voltage. The ON/OFF current ratio is more than 100, while the ideality factor,  $\eta$ , of the diode is estimated to be 1.25. Figure 3b shows the drain current–gate voltage ( $I_D$ – $V_G$ ) transfer curve of

the bottom-gate MoS<sub>2</sub> nanoflake FET at a drain–source voltage,  $V_D$ , of 0.1 V, where  $I_D$  of more than 1  $\mu$ A is obtained along with an ON/OFF current ratio of  $\sim 10^5$  and subthreshold slope (SS) of  $\sim 0.145$  V/dec. The thickness of the MoS<sub>2</sub> flake is  $\sim 32$  nm, as shown in the atomic force microscope data of Figure 3c. Our MoS<sub>2</sub> device has a gate hysteresis of less than 2 V, and its linear mobility,  $\mu$ , is around  $6$  cm<sup>2</sup>/V·s, as shown in the inset of Figure 3b, while the mobility estimation came from a well-known equation,  $\mu = (\partial I_D / \partial V_G) / (1 / (C_{ox} V_D (W/L)))$ , where  $C_{ox}$  is the dielectric capacitance ( $\sim 220$  nF/cm<sup>2</sup>) and  $W$  and  $L$  are the channel width and length, respectively (Table S1). The output curve ( $I_D$ – $V_D$ ) of Figure 3d shows an almost linear characteristic at high drain–source voltage, which indicates a good ohmic contact between Ti/Au and MoS<sub>2</sub> without any thermal annealing. As shown in Supporting Information Figure S1 and Table S1, we could also fabricate another bottom-gate MoS<sub>2</sub> FET with thinner ( $\sim 25$  nm) and thicker ( $\sim 72$  nm) MoS<sub>2</sub> flakes, using the same nanotransfer printing method and 30 nm thin ALD Al<sub>2</sub>O<sub>3</sub> for the dielectric layer. In those cases, a higher linear mobility of  $\sim 22$  cm<sup>2</sup>/V·s was achieved from the thinner MoS<sub>2</sub>, while a lower mobility of  $\sim 4$  cm<sup>2</sup>/V·s was obtained from the thicker channel. Compared to the previous reports for high mobility over 100 cm<sup>2</sup>/V·s, our MoS<sub>2</sub> FETs showed relatively lower values than those reported,<sup>6,14,16,20</sup> because our nanoflakes were much thicker than those (a few layer; 0.7–2.0 nm) with top-gate structure<sup>6,16,20</sup>

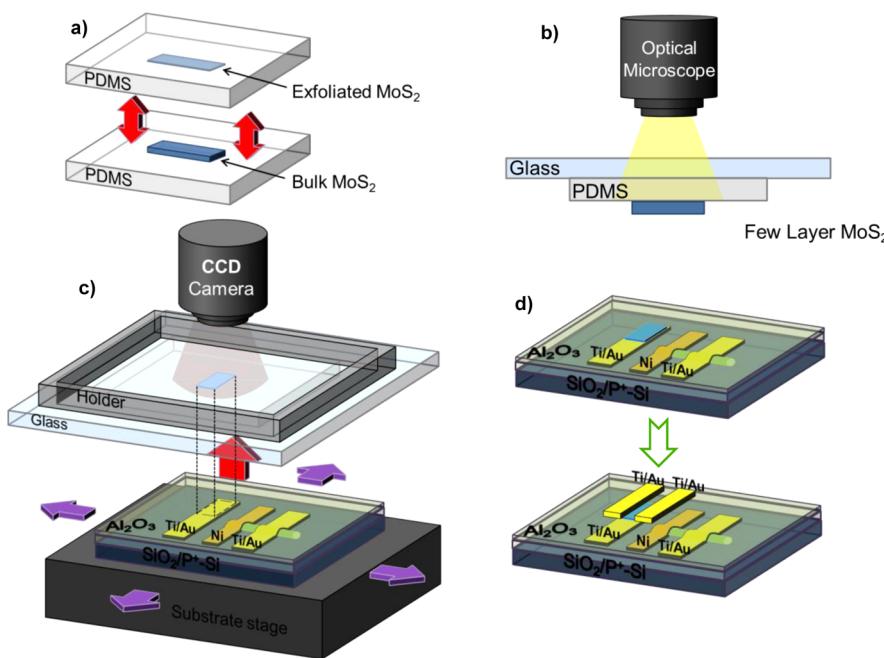

Figure 2.  $\text{MoS}_2$  nanoflake FET–ZnO nanowire diode coupled inverter: (a) schematic cross section of the inverter, (b) top-view optical microscopic image, and (c) HRSEM view of the inverter along with the circuit diagram of the FET and Schottky diode drawn over it.  $V_{DD}$ ,  $V_{IN}$ , and  $V_{OUT}$  respectively represent supply, input, and output voltages. Al wire bonding was used to connect the two individual devices on the same substrate.

Figure 3. (a) Linear and logarithm scale  $I$ – $V$  plots of Ni/ZnO nanowire Schottky diode. (b) Transfer curve of our bottom-gate patterned  $\text{MoS}_2$  nanoflake FET and  $V_G$ -dependent linear mobility plot (inset). (c) AFM line profile of the  $\text{MoS}_2$  flake showing thickness with inset indicating a portion of the flake above  $\text{Al}_2\text{O}_3$ . (d) Output curves of  $\text{MoS}_2$  nanoflake FET with inset showing the magnified low-bias linear behavior.

and also because our source–drain metal electrode (Ti/Au) would not be the best-optimized contact.<sup>21,22</sup> Almost the same amount of gate hysteresis was found from those nanoflake FETs, and the cause of such hysteresis is attributed to the surface charge state of back-channel  $\text{MoS}_2$ , which might be changed by gate bias sweep.<sup>23</sup> It is interesting that the mobility and ON current  $I_D$  of FETs decrease with thickness of  $\text{MoS}_2$ ,

This is probably because of the parasitic resistance originating from the thickness path of current, which should exist in the device architecture of the top source/drain contact bottom-gate FET as reported in conventional thin-film transistor studies.<sup>21,24,25</sup>

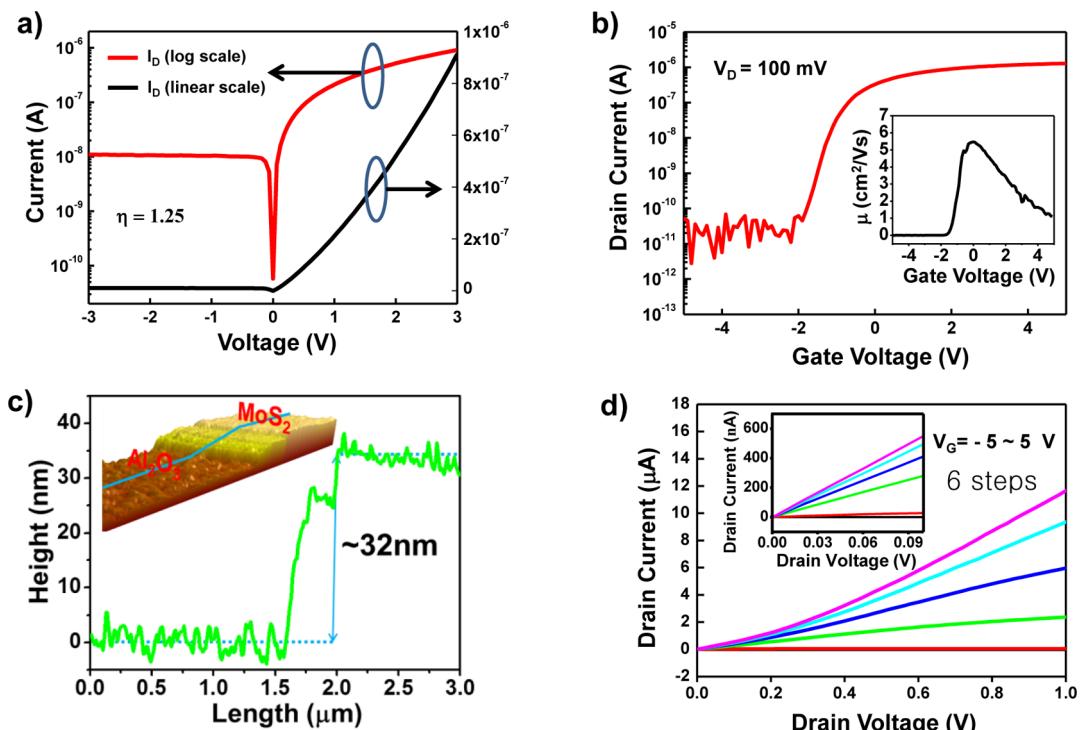

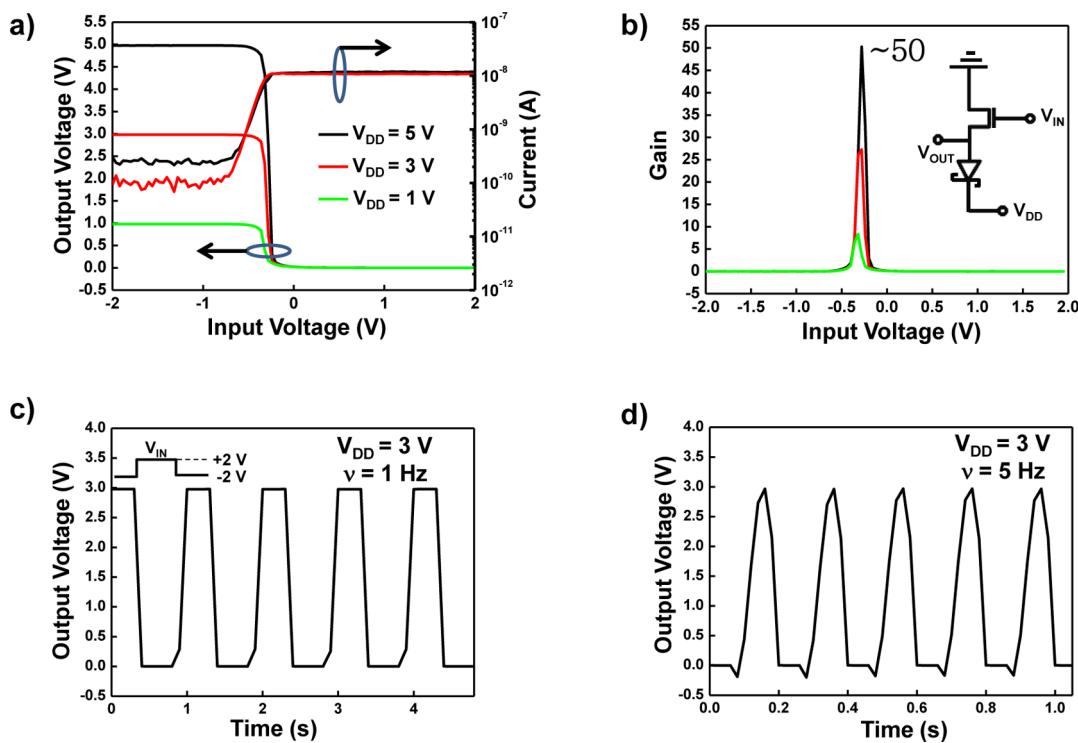

Figure 4a shows the voltage transfer curves (VTCs) of an electrical inverter formed by connecting the  $\text{MoS}_2$  nanoflake FET and ZnO Schottky diode in series; the

**Figure 4.** (a) VTCs of our ZnO nanowire–MoS<sub>2</sub> nanoflake-based hybrid inverter obtained at a  $V_{DD}$  of 1, 3, and 5 V;  $I_{DD}$  curves were also obtained at 3 and 5 V. (b) Corresponding voltage gains ( $= -dV_{OUT}/dV_{IN}$ ) of the inverter and its gate dynamics are observed under a  $V_{DD}$  of 3 V by a time domain  $V_{IN}$  pulse at (c) 1 and (d) 5 Hz; rising/falling time was as large as  $\sim 50$  ms, which is probably due to the intrinsic RC delay generated in our unoptimized device architecture with large parasitic capacitances.

inverter operation was implemented by sweeping the gate-source voltage,  $V_G$  ( $=V_{IN}$ , the input voltage of the driver in Figure 2c). The transition voltage for high and low states in VTCs appears to be  $\sim 0.5$  V, since the turn on voltage of our nanoflake FET was around  $-1$  V (Figure 3b). When three different supply voltages ( $V_{DD} = 1$ , 3, and 5 V) are applied, the ZnO diode of our hybrid inverter should be under reverse bias conditions according to the inverter circuit of Figure 2c, so that the reversed biased Schottky diode limits the inverter current ( $I_{DD}$ ) to less than 10 nA, which leads to low power consumption, less than few tens of nanowatts depending on applied supply voltage. (Estimated power consumption of 30–50 nW is quite low for a non-CMOS inverter.) According to the voltage gain ( $= -dV_{OUT}/dV_{IN}$ ) plots of Figure 4b, quite high gains of 10, 30, and 50 are exhibited for  $V_{DD}$  of 1, 3, and 5 V, respectively, which is almost the highest gain result for MoS<sub>2</sub>-based inverters ever reported until now, based on our limited knowledge.<sup>14,16,26</sup> Such high gain is probably related to the current suppression by a reverse-biased Schottky diode as well. The inverter gate dynamics of our inverter are observed under a  $V_{DD}$  of 3 V by a time domain  $V_{IN}$  pulse at 1 and 5 Hz as shown in Figure 4c and d (with rising time  $\sim 50$  ms).

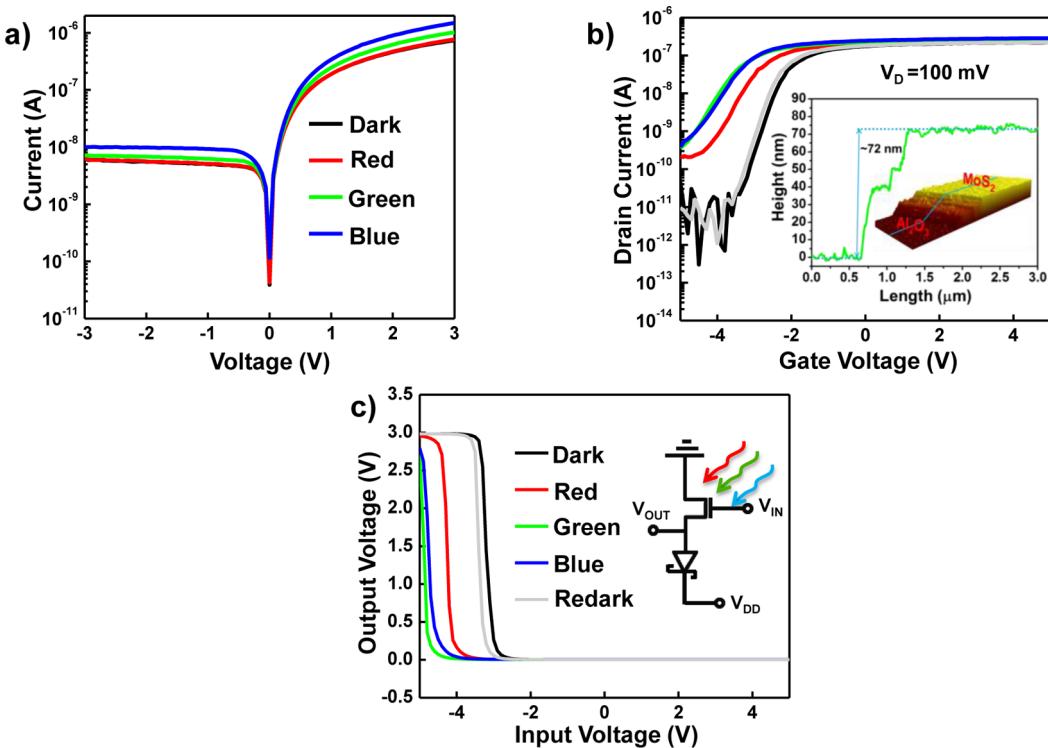

For a photosensing application, we prepared a different set of inverters with a thicker MoS<sub>2</sub> layer ( $\sim 70$  nm; Figure 5b and its inset show the MoS<sub>2</sub> thickness in AFM), which may provide some benefits

with higher quantum efficiencies under off-state gate bias, absorbing a higher number of visible photons from respective light-emitting diodes (LEDs; intensity was a few mW cm<sup>-2</sup>): red (630 nm), green (540 nm), and blue (440 nm). According to  $I$ - $V$  curves of Figure 5a and b, the ZnO nanowire Schottky diode appears quite insensitive to visible light, compared to the photoelectric behavior of the patterned MoS<sub>2</sub> FET, which shows a light-induced threshold voltage shift and large photocurrent in the phototransfer curves. The photoblindness of the ZnO Schottky diode is quite expected, because the band gap of the ZnO nanowire is as high as  $\sim 3.2$  eV, so that the nanowire mostly transmits visible light with lower energy,<sup>27,28</sup> and also because the light-exposed area of the nanowire is almost out of the electric ( $E$ )-field and any photoexcited carriers would thus be recombined with their original (trap) sites.<sup>29</sup> However, the patterned MoS<sub>2</sub> FET meets a different situation, since its band gap is around 1.2 eV, which is small enough to receive and absorb visible photons. Excited electrons are easily collected by the drain even at a low  $V_D$  of 0.1 V, to contribute to the photosignal particularly under off-state gate bias. These photocurrents are converted to a voltage signal ( $V_{OUT}$ ) when the two devices—the ZnO nanowire Schottky diode and MoS<sub>2</sub> FET—are coupled in series to form a photoinverter.

The photoinduced behavior is now shown in Figure 5c as VTCs under dark, red, green, blue, and

Figure 5. (a)  $I-V$  curves of a ZnO Schottky diode under red (R), green (G), and blue (B) illuminations. (b) Photoinduced transfer curves of a  $\text{MoS}_2$  FET with 70 nm thick  $\text{MoS}_2$  flake (inset AFM), as obtained under the same R, G, and B illuminations. (c) Photoinduced VTCs of our photoinverter and its circuit (inset).

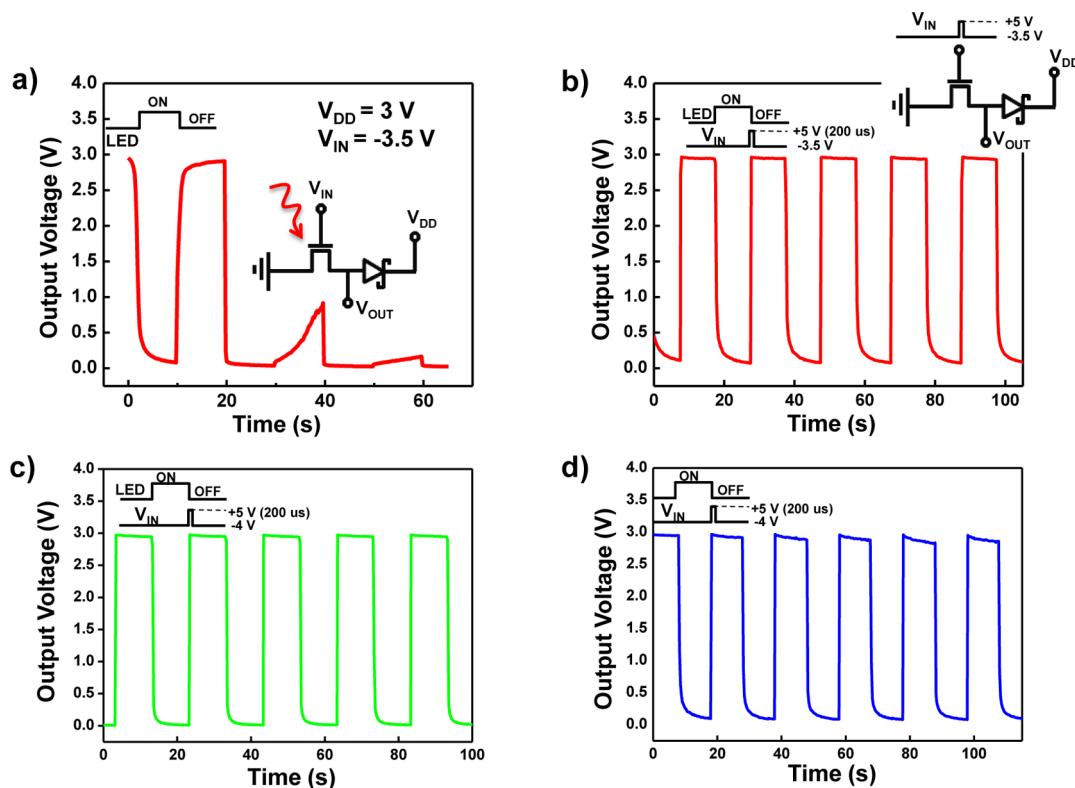

Figure 6. (a) Photoinverter dynamics under periodic illumination of red light (inset schemes and circuit) shows PPC problems in the absence of positive gate pulse. (b, c, d) However, a +5 V gate pulse of 200  $\mu\text{s}$  (inset pulse scheme) removes the PPC issues for red, green, and blue light, respectively.

redark conditions, along with inset inverter circuit (inverter supply voltage ( $V_{DD}$ ) was fixed at 3 V, and the voltage gain was  $\sim 14$ ). As the threshold voltage shift was shown in the transfer curves of Figure 5b, the photoinduced VTC curve shift is observed in Figure 5c as a reflection of the transfer curves. After switching off the illumination, our inverter device mostly recovers its initial dark behavior (the smaller shift induced by red light is probably due to the optical power differences). Since the initial dark–illumination–redark stages were reproducibly repeated in the VTC regime, we attempted a more practical application: photodynamic output voltage ( $V_{OUT}$ ) recording in a time domain. ON-and-OFF repeating of LED illumination was implemented to record  $V_{OUT}$  under a fixed input voltage ( $V_{IN}$ ) of  $-3.5$ ,  $-4$ , and  $-4$  V (respectively for red, green, and blue), while a supply voltage ( $V_{DD}$ ) was fixed at 3 V. However, any decent photoinverting dynamic output was not easy to achieve, as shown in Figure 6a for red (and Figure S2 for green and blue); persistent photoconductivity (PPC) phenomena are rather observed. The observed PPC have been explained based on a few different models including random local-potential fluctuation (RLPF) and large lattice relaxation (LLR) models, which are more applicable for 2D layered materials.<sup>13,30–34</sup> In the RLFP model, random local-potential fluctuations induced by compositional fluctuations are responsible for PPC, while in the LLR model the PPC involves photoexcitation of electrons from deep-level-like traps (DX-like centers).<sup>30</sup>

An electron-capture barrier is created by lattice relaxation, preventing recapture/recombination of electrons by these trap centers.<sup>35–38</sup> In the present work, these PPC issues were effectively resolved by using a short accumulation (on-state) voltage pulse

(by less than  $200\ \mu s$  short gate pulse), as clearly shown in Figure 6b, c, and d for red, green, and blue illumination. According to the inset pulse schemes in the figures, short positive gate pulses (to  $+5$  V) are instantaneously applied to accumulate electrons at the interface region, immediately after the light exposure. This positive gate pulse process accelerates the recombination process and suppresses the electron-capture barrier. The trap-induced transient  $I_D$  may rapidly fall to the initial dark value by the gate pulse, and as a result, our photoinverter shows a short recovery time of less than 0.2 s, ensuring somewhat desirable behavior of the dynamic photodetector.

## CONCLUSION

In summary, by using a nanotransfer printing method and conventional lithography, we have conveniently fabricated a 1D–2D hybrid inverter composed of a ZnO nanowire Schottky diode and a MoS<sub>2</sub> nanoflake patterned bottom-gate FET. The ZnO nanowire Schottky diode and MoS<sub>2</sub> FET worked respectively as load and driver for a logic inverter, which exhibits a high voltage gain of  $\sim 50$  at a  $V_{DD}$  of 5 V and also shows a low power consumption of less than 50 nW mainly due to the presence of a reverse-biased Schottky diode. In addition, our inverter effectively operates as a photoinverter, detecting visible photons, since MoS<sub>2</sub> FETs appear very photosensitive, while the serially connected ZnO nanowire Schottky diode was blind to visible light. The PPC issue in the MoS<sub>2</sub> FET was resolved by using a small positive pulse at the gate terminal soon after light exposure. We conclude that our 1D–2D hybrid photoinverter is quite promising for both logic and photosensing inverters with high device performances.

## METHODS

To fabricate the hybrid inverter, we coupled a ZnO nanowire Schottky diode with a MoS<sub>2</sub> nanoflake FET. A p<sup>+</sup>-Si/SiO<sub>2</sub> wafer was ultrasonically cleaned in acetone, methyl alcohol, and deionized water, to be used as a substrate. On the surface of the oxygen plasma-treated substrate, the drop and dry method was used to disperse the nanowires that were in the isopropyl alcohol solution. The Ti/Au electrode was used for the good ohmic contact metal of the 200 nm thick ZnO nanowire<sup>39</sup> and for the bottom gate of the MoS<sub>2</sub> FET as well. These were patterned using the photolithography process described elsewhere.<sup>40</sup> A 25 nm thin Ti layer and a Au layer (Ti/Au) for the ohmic electrode were sequentially deposited on ZnO nanowires using a dc-magnetron sputtering system, which was followed by a lift-off process. For the lift-off process, acetone and lift-off layer (LOL) remover solvents were used. The same process was carried out to form Schottky contacts of e-beam deposited 100 nm thick Ni on the ZnO nanowire. Then, in order to passivate the ZnO nanowire Schottky diode and simultaneously to fabricate a dielectric layer for the MoS<sub>2</sub> nanoflake FET, we deposited 30 nm thin ALD Al<sub>2</sub>O<sub>3</sub> on the whole device area. Using polydimethylsiloxane (PDMS) stamps, we now transferred the MoS<sub>2</sub> nanoflake on the bottom-gate ALD Al<sub>2</sub>O<sub>3</sub> dielectric, so that our MoS<sub>2</sub> flake might also be aligned

on the Ti/Au back-gate electrode, which was already patterned beneath Al<sub>2</sub>O<sub>3</sub>. We named this transfer process as nanotransfer printing, of which more details can be found in our recent report.<sup>41</sup>

Figure 1a–d show the nanotransfer printing processes that include flake exfoliation, gate metal locating, aligning, and printing on the gate metal. Instead of Scotch tape, PDMS stamps were used to exfoliate the MoS<sub>2</sub> flakes, as shown in Figure 1a. After exfoliation, many flakes were carried on the glass support, as attached on the PDMS. Among the flakes, an optimally thin flake was chosen by an optical microscope (see Figure 1b), although the optical microscope search usually selected a little thicker MoS<sub>2</sub> ranging from  $\sim 10$  to  $\sim 80$  nm in thickness. Then the optimum flake on the PDMS sample was aligned above a 30 nm thin Al<sub>2</sub>O<sub>3</sub> dielectric/gate electrode by using an optical microscope and CCD camera-equipped microaligner, as shown in Figure 1c, where four arrows indicate stage translation directions for device alignment. The MoS<sub>2</sub> layer was aligned above the patterned bottom gate (which is the target place near the ZnO nanowire diode) and then attached by imprinting (suppressing the stage) as shown by the red arrow in Figure 1c. The upper part of Figure 1d shows the result of such nanotransfer printing; a schematic structure of the MoS<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> dielectric–Ti/Au gate is shown along with Ni–ZnO nanowire

Schottky diode. Finally, 100 nm thick Ti/Au source/drain ohmic contacts were formed on the  $\text{MoS}_2$  flake by using a similar lift-off process to that implemented to one side of the  $\text{ZnO}$  nanowire Schottky diode, to finalize the whole device process (see the lower part of Figure 1d).

Inverter formation was simply realized by connecting the Ti/Au drain contact of the  $\text{MoS}_2$  nanoflake FET to the Ni Schottky contact of the  $\text{ZnO}$  diode; the final electrical connection was realized by wire bonding. Figure 2a shows the schematic cross section of the inverter coupling the bottom-gate  $\text{MoS}_2$  nanoflake FET and the  $\text{ZnO}$  nanowire source/drain, while the top-view microscopy images (optical and high-resolution scanning electron microscopies (HRSEM)) are presented in Figure 2b and c, where an inverter circuit drawing is overlaid. The channel length,  $L$ , of the  $\text{MoS}_2$  FET was  $3 \mu\text{m}$ , while our  $\text{ZnO}$  nanowire diameter was  $\sim 200 \text{ nm}$  and the length was around  $30 \mu\text{m}$ , which allowed us to fabricate an array of diodes in each substrate. All device characterizations were performed in the dark at room temperature using a semiconductor parameter analyzer (HP4155C, Agilent Technologies), and a function generator (AFG 310, Tektronix) was used for dynamic measurements on the  $\text{MoS}_2$  nanoflake FETs.

*Conflict of Interest:* The authors declare no competing financial interest.

*Acknowledgment.* The authors acknowledge the financial support from NRF (NRL program: Grant No. 2009-0079462), Nanomaterial Technology Development Program through the NRF of Korea (Grant No. 2012M3A7B4034985), and Brain Korea 21 Plus Program.

*Supporting Information Available:* Transfer curve, output curve, and thickness measurement of 25 nm thin  $\text{MoS}_2$  nanoflake FET, table of information including thickness, mobility,  $W/L$  ratio,  $I_{\text{on/off}}$ ,  $I_{\text{on}}$ , and  $V_D$ , and photoinverter dynamics under green and blue LED illumination without gate pulse. This material is available free of charge via the Internet at <http://pubs.acs.org>.

## REFERENCES AND NOTES

- Schwierz, F. Graphene Transistors. *Nat. Nanotechnol.* **2010**, *5*, 487–496.

- Bolotin, K. I.; Sikes, K. J.; Jiang, Z.; Klima, M.; Fudenberg, G.; Hone, J.; Kim, P.; Stormer, H. L. Ultrahigh Electron Mobility in Suspended Graphene. *Solid State Commun.* **2008**, *146*, 351–355.

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Ann. N.Y. Acad. Sci.* **2004**, *306*, 666–669.

- Berger, C.; Song, Z.; Li, T.; Li, X.; Ogbazghi, A. Y.; Feng, R.; Dai, Z.; Marchenkov, A. N.; Conrad, E. H.; First, P. N.; et al. Ultrathin Epitaxial Graphite: 2D Electron Gas Properties and a Route toward Graphene-Based Nanoelectronics. *J. Phys. Chem. B* **2004**, *108*, 19912–19916.

- Coleman, J. N.; Lotya, M.; O'Neill, A.; Bergin, S. D.; King, P. J.; Khan, U.; Young, K.; Gaucher, A.; De, S.; Smith, R. J. Two-Dimensional Nanosheets Produced by Liquid Exfoliation of Layered Materials. *Science* **2011**, *331*, 568–571.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer  $\text{MoS}_2$  Transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- Eda, G.; Yamaguchi, H.; Voiry, D.; Fujita, T.; Chen, M.; Chhowalla, M. Photoluminescence from Chemically Exfoliated  $\text{MoS}_2$ . *Nano Lett.* **2011**, *11*, 5111–5116.

- Han, S. W.; Kwon, H.; Kim, S. K.; Ryu, S.; Yun, W. S.; Kim, D. H.; Hwang, J. H.; Kang, J. S.; Baik, J.; Shin, H. J.; et al. Band-Gap Transition Induced by Interlayer van der Waals Interaction in  $\text{MoS}_2$ . *Phys. Rev. B* **2011**, *84*, 045409.

- Lee, H. S.; Min, S.-W.; Chang, Y.-G.; Park, M. K.; Nam, T.; Kim, H.; Kim, J. H.; Ryu, S.; Im, S.  $\text{MoS}_2$  Nanosheet Phototransistors with Thickness-Modulated Optical Energy Gap. *Nano Lett.* **2012**, *12*, 3695–3700.

- Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin  $\text{MoS}_2$ : A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* **2010**, *105*, 136805.

- Splendiani, A.; Sun, L.; Zhang, Y.; Li, T.; Kim, J.; Chim, C.-Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer  $\text{MoS}_2$ . *Nano Lett.* **2010**, *10*, 1271–1275.

- Choi, W.; Cho, M. Y.; Konar, A.; Lee, J. H.; Cha, G. B.; Hong, S. C.; Kim, S.; Kim, J.; Jena, D.; Joo, J. High-Detectivity Multilayer  $\text{MoS}_2$  Phototransistors with Spectral Response from Ultraviolet to Infrared. *Adv. Mater.* **2012**, *24*, 5832–5836.

- Lopez-Sanchez, O.; Lembke, D.; Kayci, M.; Radenovic, A.; Kis, A. Ultrasensitive Photodetectors Based on Monolayer  $\text{MoS}_2$ . *Nat. Nanotechnol.* **2013**, *8*, 497–501.

- Radisavljevic, B.; Whitwick, M. B.; Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer  $\text{MoS}_2$ . *ACS Nano* **2011**, *5*, 9934–9938.

- Radisavljevic, B.; Whitwick, M. B.; Kis, A. Small-Signal Amplifier Based on Single-Layer  $\text{MoS}_2$ . *Appl. Phys. Lett.* **2012**, *101*, 043103.

- Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer  $\text{MoS}_2$  Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

- Zhang, W.; Huang, J. K.; Chen, C. H.; Chang, Y. H.; Cheng, Y. J.; Li, L. J. High-Gain Phototransistors Based on a CVD  $\text{MoS}_2$  Monolayer. *Adv. Mater.* **2013**, *25*, 3456–3461.

- Huang, J.; Somu, S.; Busnaina, A. A Molybdenum Disulfide/Carbon Nanotube Heterogeneous Complementary Inverter. *Nanotechnology* **2012**, *23*, 335203.

- Jariwala, D.; Sangwan, V. K.; Wu, C.-C.; Prabhumirashi, P. L.; Geier, M. L.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. Gate-Tunable Carbon Nanotube– $\text{MoS}_2$  Heterojunction p-n Diode. *Proc. Natl. Acad. Sci. U.S.A.* **2013**, *110*, 18076–18080.

- Min, S.-W.; Lee, H. S.; Choi, H. J.; Park, M. K.; Nam, T.; Kim, H.; Ryu, S.; Im, S. Nanosheet Thickness-Modulated  $\text{MoS}_2$  Dielectric Property Evidenced by Field-Effect Transistor Performance. *Nanoscale* **2013**, *5*, 548–551.

- Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer  $\text{MoS}_2$  Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

- Dankert, A.; Langouche, L.; Kamalakar, M. V.; Dash, S. P. High-Performance Molybdenum Disulfide Field-Effect Transistors with Spin Tunnel Contacts. *ACS Nano* **2014**, *8*, 476–482.

- Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer  $\text{MoS}_2$  Field Effect Transistors. *ACS Nano* **2012**, *6*, 5635–5641.

- Saudari, S. R.; Lin, Y. J.; Lai, Y.; Kagan, C. R. Device Configurations for Ambipolar Transport in Flexible, Pentacene Transistors. *Adv. Mater.* **2010**, *22*, 5063–5068.

- Lee, J.; Kim, K.; Kim, J. H.; Im, S.; Jung, D.-Y. Optimum Channel Thickness in Pentacene-Based Thin-Film Transistors. *Appl. Phys. Lett.* **2003**, *82*, 4169–4171.

- Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. *ACS Nano* **2014**, *1102*–1120.

- Djurisic, A. B.; Leung, Y. H. Optical Properties of  $\text{ZnO}$  Nanostructures. *Small* **2006**, *2*, 944–961.

- Rühle, S.; Van Vugt, L.; Li, H.-Y.; Keizer, N.; Kuipers, L.; Vanmaekelbergh, D. Nature of Sub-Band Gap Luminescent Eigenmodes in a  $\text{ZnO}$  Nanowire. *Nano Lett.* **2008**, *8*, 119–123.

- Ryu, B.; Lee, Y. T.; Lee, K. H.; Ha, R.; Park, J. H.; Choi, H.-J.; Im, S. Photostable Dynamic Rectification of One-Dimensional Schottky Diode Circuits with a  $\text{ZnO}$  Nanowire Doped by H during Passivation. *Nano Lett.* **2011**, *11*, 4246–4250.

- López Sánchez, O. *Single-Layer Molybdenum Disulfide Photodetectors*; Universitat Politècnica de Catalunya: Barcelona, 2012; pp 43–53.

- Zhang, W.; Huang, J.-K.; Chen, C.-H.; Chang, Y.-H.; Cheng, Y.-J.; Li, L.-J. High-Gain Phototransistors Based on a CVD  $\text{MoS}_2$  Monolayer. *Adv. Mater.* **2013**, *25*, 3456–3461.

- Lee, Y. C.; Shen, J. L.; Chen, K. W.; Lee, W. Z.; Hu, S. Y.; Tiong, K. K.; Huang, Y. S. Observation of Persistent Photoconductivity in 2H- $\text{MoSe}_2$  Layered Semiconductors. *J. Appl. Phys.* **2006**, *99*, 063706.

33. Roy, K.; Padmanabhan, M.; Goswami, S.; Sai, T. P.; Ramalingam, G.; Raghavan, S.; Ghosh, A. Graphene-MoS<sub>2</sub> Hybrid Structures for Multifunctional Photoresponsive Memory Devices. *Nat. Nanotechnol.* **2013**, *8*, 826–830.

34. Cunningham, G.; Khan, U.; Backes, C.; Hanlon, D.; McCloskey, D.; Donegan, J. F.; Coleman, J. N. Photoconductivity of Solution-Processed MoS<sub>2</sub> Films. *J. Mater. Chem. C* **2013**, *1*, 6899–6904.

35. Janotti, A.; Van de Walle, C. G. Oxygen Vacancies in ZnO. *Appl. Phys. Lett.* **2005**, *87*, 122102.

36. Jeon, S.; Ahn, S.-E.; Song, I.; Kim, C. J.; Chung, U.-I.; Lee, E.; Yoo, I.; Nathan, A.; Lee, S.; Robertson, J. Gated Three-Terminal Device Architecture to Eliminate Persistent Photoconductivity in Oxide Semiconductor Photosensor Arrays. *Nat. Mater.* **2012**, *11*, 301–305.

37. Lany, S.; Zunger, A. Anion Vacancies as a Source of Persistent Photoconductivity in II-VI and Chalcopyrite Semiconductors. *Phys. Rev. B* **2005**, *72*, 035215.

38. Ali Raza, S. R.; Lee, Y. T.; Hosseini Shokouh, S. H.; Ha, R.; Choi, H.-J.; Im, S. A ZnO Nanowire-Based Photo-Inverter with Pulse-Induced Fast Recovery. *Nanoscale* **2013**, *5*, 10829–10834.

39. Brillson, L. J.; Lu, Y. ZnO Schottky Barriers and Ohmic Contacts. *J. Appl. Phys.* **2011**, *109*, 121301–121301–33.

40. Lee, Y. T.; Ali Raza, S. R.; Jeon, P. J.; Ha, R.; Choi, H.-J.; Im, S. Long Single ZnO Nanowire for Logic and Memory Circuits: NOT, NAND, NOR Gate, and SRAM. *Nanoscale* **2013**, *5*, 4181–4185.

41. Choi, K.; Lee, Y. T.; Min, S.-W.; Lee, H. S.; Nam, T.; Kim, H.; Im, S. Direct Imprinting of MoS<sub>2</sub> Flakes on a Patterned Gate for Nanosheet Transistors. *J. Mater. Chem. C* **2013**, *1*, 7803–7807.